Beginners Guide to FPGA Design

How to Begin a Simple FPGA Design?

Catalog | |

Ⅰ Overview

FPGAs are more widely used than we imagine because there are more kinds of integrated modules than just the original simple logic unit (LE).

Early FPGAs were relatively simple, and all functional units were built only from pins, internal buffer, LE, RAM, LE consisted of LUT (lookup table) and D flip-flop, and RAM also tended to have very small capacity.

Nowadays, FPGAs not only include the previous LE. RAM is also larger, faster, and more flexible, the IOB is also more complex and supports more IO types, and also integrates some special functional units, including the following units.

DSP: It actually is the multiplier. FPGA can integrate multiple multipliers, while the general DSP chip often only one per core. In other words, FPGAs can more easily implement multiple DSP core functions. In some cases where a large number of multiplication and addition calculations are required, the speed of multiple multiplicators working in parallel can be much faster than one high-speed multiplicator.

SERDES: High-speed serial interface. In the future, there will be more and more high-speed serial interfaces such as PCI-E, XAUI, HT, and S-ATA. With SERDES module, FPGAs can easily integrate these high-speed serial interfaces, without the need to purchase special interface chips.

CPU core: There are 2 kinds of CPU core, soft core and hard core. Soft core is a CPU module written in logic code, which can be implemented in any FPGA with sufficient resources and is very flexible to use. Moreover, multiple soft cores can be integrated in a large-capacity FPGA to achieve multi-core parallel processing. The hard core is a CPU core made inside a specific FPGA, which has the advantage of fast speed and good performance, but it is not flexible enough.

However, FPGA still has disadvantages. For some high main frequency applications, FPGA can't work normally. Now although theoretically, the FPGA can support 500MHz, but in the actual design, more than 200MHz operating frequency is very difficult to achieve.

Ⅱ Four main points of FPGA design

1. The clock tree

For FPGAs, asynchronous design should be avoided as much as possible, and synchronous design should be used as much as possible.

The first key to synchronous design, and the key of keys, is the clock tree.

A bad clock tree, for FPGA design, is an irreparable disaster, is a building without a good foundation, and the collapse is inevitable.

Some specific design details:

1) Use a single clock whenever possible.

2) If there are multiple clock domains, you must be carefully divided.

3) The signal across the clock domain must do synchronization processing. For the control signal, you can use double sampling; for the data signal, you can use asynchronous fifo. It should be noted that asynchronous fifo is not a panacea. An asynchronous fifo can only solve a certain range of frequency difference problems.

4) The internal PLL and DLL of FPGA should be utilized as far as possible, which will bring a lot of benefits to your design.

5) For special IO interface, you need to carefully calculate Tsu, Tco, Th, and use PLL, DLL, DDIO, pin settable delays, and other tools. Simple constraints on the pins Tsu, Tco, Th are often not possible.

Here the clock tree actually refers to the clock scheme, mainly the clock domain and PLL planning. In general, it does not involve the detailed calculation of the alignment delay (generally go to the global clock network and local clock network, the delay is fixed), and the ASIC clock tree is not the same. For ASIC, the clock network design, wiring, delay calculations must be carefully analyzed to calculate.

FPGA development and design process

2. FSM

FSM: finite state machine. This can be said to be the basis of logic design.

FSM is divided into moore type and merly type. Moore type state migration and variables are not related, merly type is related. The moore type has nothing to do with variable migration, while the merly type has everything to do with it. In practice, the merly type is mostly used.

There are two ways to write FSM: single-process and dual-process.

Beginners tend to prefer the single-process method, with the following format.

always @ (posedge clk or posedge rst)

begin

if (rst == 1'b1 )

FSM_status <= .......

else

case ( FSM_status )

.......

endcase

end

Simply put, a single-process FSM is one that puts all synchronous and asynchronous processing into one always.

Advantages

1) It looks simple and clear, and you don't have to write all the processing of each signal and status signal in each case branch or if branch. You can also simply add some counters to it for counting.

2) All output signals are already latching by D flip-flop.

Disadvantages

1) Poor optimization. Since synchronous and asynchronous are put together, the compiler generally optimizes the asynchronous logic best. The result of single-process FSM mixing synchronous and asynchronous together is that it leads to poor compiler optimization, often resulting in slow logic and high resource consumption.

2) Sometimes, faster signal output is needed without having to go through the D flip-flop latch, which is more troublesome to handle with single-process FSM.

Dual-process FSM with the following format.

always @ (posedge clk or posedge rst )

begin

if (rst == 1'b1 )

FSM_status_current <= ....

else

FSM_status_current <= FSM_status_next;

always @ (*)

begin

case (FSM_status_current )

FSM_status_next = .......

endcase

end

From the above, we can see that synchronous and asynchronous processing are put into 2 always. The FSM status variables are also controlled by two of them. I won't go into the principle of the dual-process FSM here, as it is described in many logic design books. It would be too much effort to describe it here.

Advantages

1) Compiler optimizations are obvious, and you can get a very desirable speed and resource usage.

2) All output signals (except FSM_status_current) are combined output, which is faster than single process FSM.

Disadvantages

1) All output signals (except FSM_status_current) are combined output, which requires extra code to be written for latching in some occasions.

2) In the always of asynchronous processing, all the if and case branches must assign all the output signals, and there cannot be a case that the output signals in the FSM are assigned back to other signals in this FSM, otherwise latch will occur.

The latch will lead to the following problems.

1) The functional simulation result does not match with the post-imitation.

2) Untestable logic.

3) Unstable logic operation, especially the latch part is unusually sensitive to burrs.

4) Some of its special cases, if positive feedback, may lead to disastrous consequences.

3. Latch

Let's talk about how to avoid the harm of latch.

(1) In the combined logic process, if statements must have else! And all signals should be assigned in all branches of if.

always @ ( * ) begin

if (sig_a == 1'b1 ) sig_b = sig_c;

end

This is definitely going to generate a latch.

The correct one should be

always @ ( * ) begin

if (sig_a == 1'b1 ) sig_b = sig_c;

else sig_b = sig_d;

end

Also, note that the following also generates latches. This means that the combinatorial logic process cannot assign itself to itself or indirectly assign itself to itself.

always @ ( * ) begin

if (rst == 1'b1 ) counter = 32'h00000000;

else counter = counter + 1;

end

However, if it is a temporal logic process, the problem does not exist.

(2) The default of the case statement must not be omitted.

The reason is the same as the if statement. Remind that in the temporal logic process, default statement must also be added, which is a good habit.

(3) Combination logic process sensitive variables can not be less nor more.

This problem is not too big, verilog2001 syntax can be directly with * done.

By the way, latch has disadvantages must be beneficial. In the FPGA LE, there is always a latch and a D flip-flop. There is also a latch in the IOE (IOB) that supports DDR to implement DDIO. However, in our usual design, we should avoid the latch as much as possible.

4. Logic simulation

Simulation is an essential step in FPGA design. Without simulation, there is nothing.

Simulation is divided into the unit simulation, integrated simulation, and system simulation.

Unit simulation: Simulation for each of the smallest basic modules. Unit simulation requires that code line coverage, conditional branch coverage, and expression coverage must reach 100%. All three coverage rates can be viewed through MODELSIM, but need to be set in the Compile option when compiling the module.

Integrated simulation: Combine several large modules together for simulation. The coverage requirement is as high as possible.

System simulation: Simulation of the entire hardware system together. In this case, the whole simulation platform includes the simulation model of the logic peripheral chip interface, as well as BFM, Testbench, etc. System simulation requires careful design of simulation test cases and simulation test platforms according to the functional and performance requirements of the logic being simulated. System simulation is a large branch of logic design and is a discipline that requires specialized study.

1. What is FPGA design?

Field Programmable Gate Arrays (FPGAs) are semiconductor devices that are based around a matrix of configurable logic blocks (CLBs) connected via programmable interconnects. FPGAs can be reprogrammed to desired application or functionality requirements after manufacturing.

2. What does an FPGA design engineer do?

FPGA Engineers work to program, design, and develop FPGA logic chips for use in day to day applications such as medical, security, or communications.

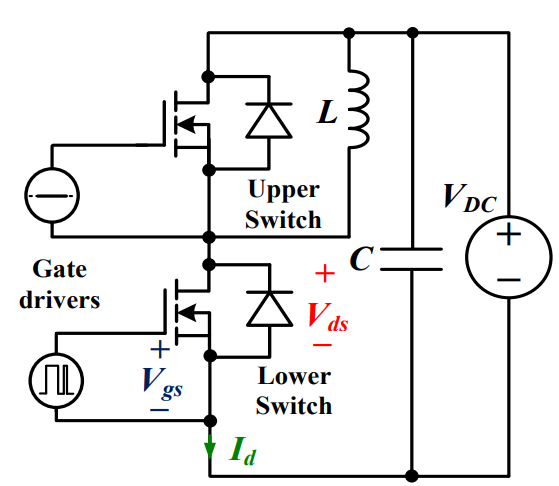

Discovering New and Advanced Methodology for Determining the Dynamic Characterization of Wide Bandgap DevicesSaumitra Jagdale15 March 20242470

Discovering New and Advanced Methodology for Determining the Dynamic Characterization of Wide Bandgap DevicesSaumitra Jagdale15 March 20242470For a long era, silicon has stood out as the primary material for fabricating electronic devices due to its affordability, moderate efficiency, and performance capabilities. Despite its widespread use, silicon faces several limitations that render it unsuitable for applications involving high power and elevated temperatures. As technological advancements continue and the industry demands enhanced efficiency from devices, these limitations become increasingly vivid. In the quest for electronic devices that are more potent, efficient, and compact, wide bandgap materials are emerging as a dominant player. Their superiority over silicon in crucial aspects such as efficiency, higher junction temperatures, power density, thinner drift regions, and faster switching speeds positions them as the preferred materials for the future of power electronics.

Read More A Comprehensive Guide to FPGA Development BoardsUTMEL11 September 202514681

A Comprehensive Guide to FPGA Development BoardsUTMEL11 September 202514681This comprehensive guide will take you on a journey through the fascinating world of FPGA development boards. We’ll explore what they are, how they differ from microcontrollers, and most importantly, how to choose the perfect board for your needs. Whether you’re a seasoned engineer or a curious hobbyist, prepare to unlock new possibilities in hardware design and accelerate your projects. We’ll cover everything from budget-friendly options to specialized boards for image processing, delve into popular learning paths, and even provide insights into essential software like Vivado. By the end of this article, you’ll have a clear roadmap to navigate the FPGA landscape and make informed decisions for your next groundbreaking endeavor.

Read More Applications of FPGAs in Artificial Intelligence: A Comprehensive GuideUTMEL29 August 20253607

Applications of FPGAs in Artificial Intelligence: A Comprehensive GuideUTMEL29 August 20253607This comprehensive guide explores FPGAs as powerful AI accelerators that offer distinct advantages over traditional GPUs and CPUs. FPGAs provide reconfigurable hardware that can be customized for specific AI workloads, delivering superior energy efficiency, ultra-low latency, and deterministic performance—particularly valuable for edge AI applications. While GPUs excel at parallel processing for training, FPGAs shine in inference tasks through their adaptability and power optimization. The document covers practical implementation challenges, including development complexity and resource constraints, while highlighting solutions like High-Level Synthesis tools and vendor-specific AI development suites from Intel and AMD/Xilinx. Real-world applications span telecommunications, healthcare, autonomous vehicles, and financial services, demonstrating FPGAs' versatility in mission-critical systems requiring real-time processing and minimal power consumption.

Read More 800G Optical Transceivers: The Guide for AI Data CentersUTMEL24 December 20253832

800G Optical Transceivers: The Guide for AI Data CentersUTMEL24 December 20253832The complete guide to 800G Optical Transceiver standards (QSFP-DD vs. OSFP). Overcome supply shortages and scale your AI data center with Utmel Electronic.

Read More Xilinx FPGAs: From Getting Started to Advanced Application DevelopmentUTMEL09 September 20254299

Xilinx FPGAs: From Getting Started to Advanced Application DevelopmentUTMEL09 September 20254299This guide is your comprehensive roadmap to understanding and mastering the world of Xilinx FPGA technology. From selecting your first board to deploying advanced AI applications, we'll cover everything you need to know to unlock the potential of these remarkable devices. The global FPGA market is on a significant growth trajectory, expected to expand from USD 8.37 billion in 2025 to USD 17.53 billion by 2035. This surge is fueled by the relentless demand for high-performance, adaptable computing in everything from 5G networks and data centers to autonomous vehicles and the Internet of Things (IoT). This guide will walk you through the key concepts, tools, and products in the Xilinx ecosystem, ensuring you're well-equipped to be a part of this technological revolution.

Read More

Subscribe to Utmel !

![UCC5310MCDR]() UCC5310MCDR

UCC5310MCDRTexas Instruments

![1EDI20H12AHXUMA1]() 1EDI20H12AHXUMA1

1EDI20H12AHXUMA1Infineon Technologies

![1EDI60H12AHXUMA1]() 1EDI60H12AHXUMA1

1EDI60H12AHXUMA1Infineon Technologies

![1EDI30I12MFXUMA1]() 1EDI30I12MFXUMA1

1EDI30I12MFXUMA1Infineon Technologies

![UCC21220DR]() UCC21220DR

UCC21220DRTexas Instruments

![HCS201T-I/SN]() HCS201T-I/SN

HCS201T-I/SNMicrochip Technology

![ADATE305BSVZ]() ADATE305BSVZ

ADATE305BSVZAnalog Devices Inc.

![AD9172BBPZ]() AD9172BBPZ

AD9172BBPZAnalog Devices Inc.

![ADUM4223CRWZ]() ADUM4223CRWZ

ADUM4223CRWZAnalog Devices Inc.

![FM33256B-G]() FM33256B-G

FM33256B-GCypress Semiconductor Corp

Product

Product Brand

Brand Articles

Articles Tools

Tools